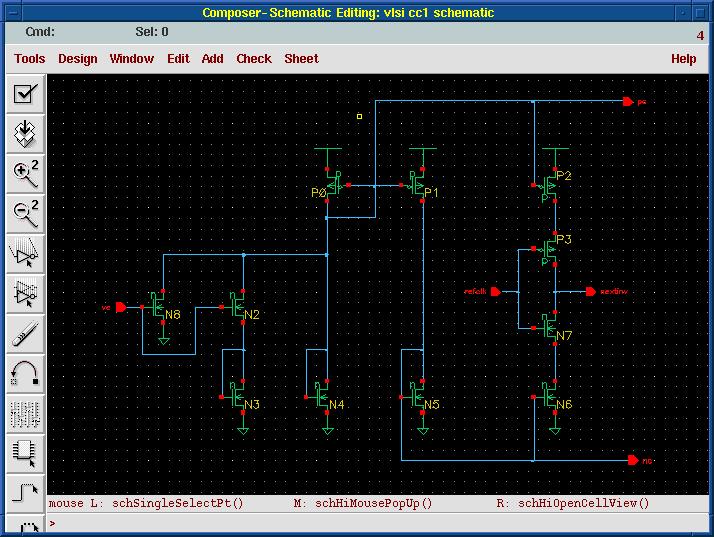

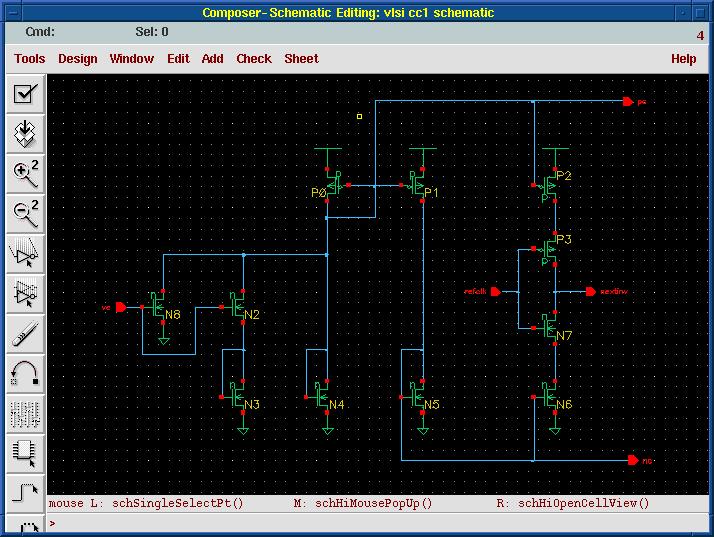

Voltage Control Delay Line:

此電路是由定電流電路及64級的反向器所組成,每二級反向器的輸出即接到多工器,以產生

不同的時序供給其它電路使用﹐其基本電路如下圖所示,其中64級的反向器以一級來作代表。

其基本操作原理是N8,N2,N3三顆的導通與截止狀態來補償定電流電路由於非線性元件,

所引起非線性電路的效應,以得到較寬的鎖相範圍,較低的jitter,及較短的鎖相時間。

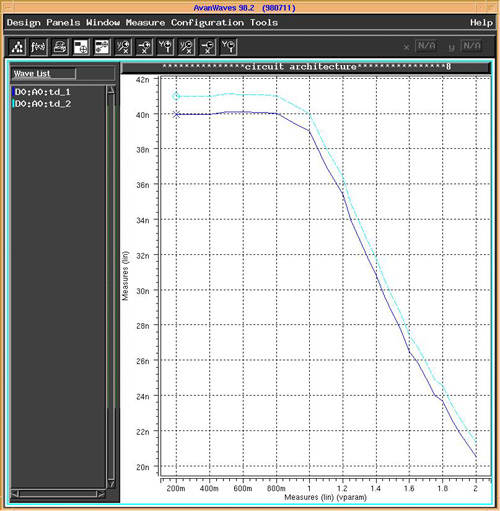

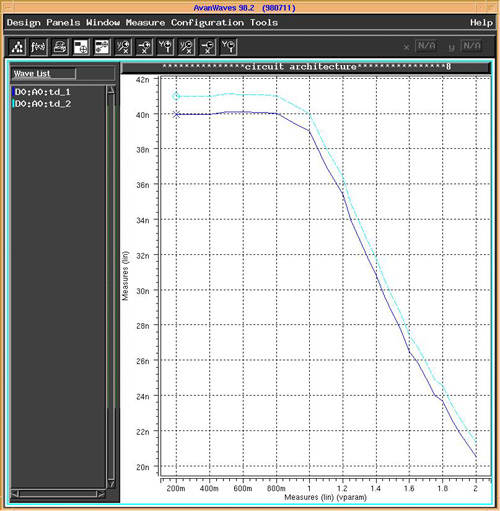

在調整過每顆MOS的W/L後,經spice模擬之後可得如下之圖形:

我們可以得到1V~2V的線性區間,即40ns(25MHz) to 22ns(45MHz),此區間為本系統最佳的操作範圍。

為何要如此注重此線性區間呢?因為線性區間越大,我們系統的lock範圍便可加大,

而且在相位相差甚多時lock time也能隨之縮小,所以此一線性區間越大越好。

回上一頁