Over All System:

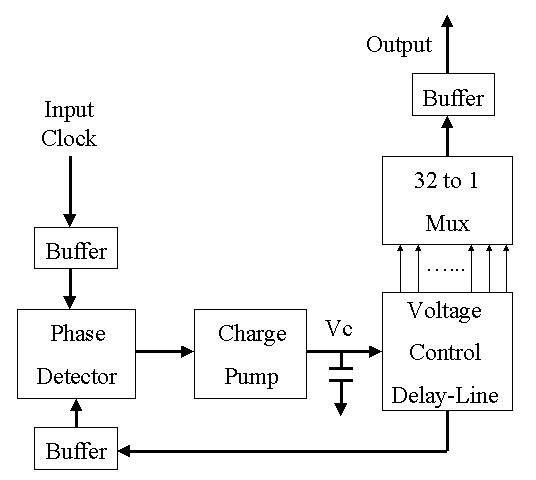

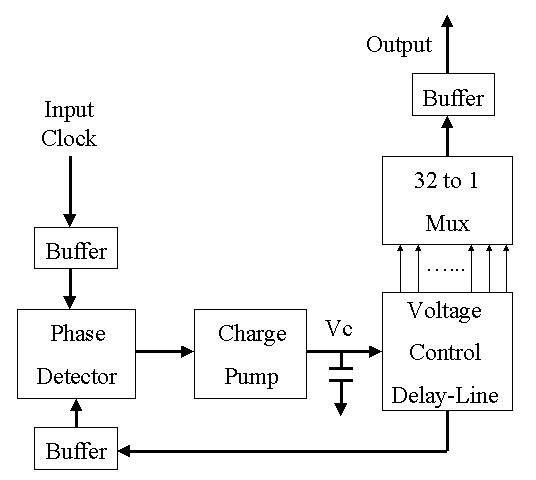

本晶片主要是由一相位偵測器(phase detector)、charge pump、及一電壓控制延遲電路

(voltage controlled delay line)所構成,如下圖所示。

本系統最主要的部份為phase detector,其構造基本上只是一個D-FF。由phase detector來判斷輸入的time及

time經過Delay Line的後的輸出其相位的關係,判斷其為領先或落後,將此領先或落後的信號經由charge pump對外接的

電容充電,再以此外接電容的儲存電量控制delay line的延遲時間長短,達成兩者信號同相位,即為lock。

而外接電容乃是考慮到系統所需之電容值較大不宜內建,因此採取外接的方法來達成,並且此一外接電容

初始值設在1.5V(Vdd/2)。

本人所設計的delay line為32級,但由於pin腳數目不夠,因此加上一個 32 to 1 的多工器,來取出我們所要的

相位訊號。並於每個輸出端皆已內建一個buffer,避免訊號強度不夠或loading太重而無法取出。

回上一頁